Arhitectura Cell Broadband Engine

Descrierea arhitecturii Cell Broadband Engine

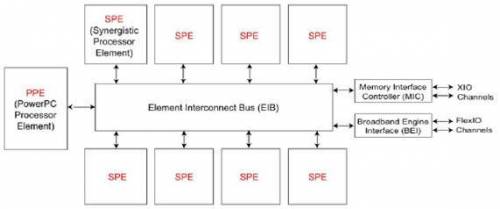

- Element Interconnect Bus (EIB). Procesorul PPE si SPEurile comunica in mod coerent intre ele, cu spatiul principal de stocare (main storage) si cu elementele I/O prin intermediul magistralei EIB. Magistrala EIB are o structura bazata pe 4 inele (doua in sens orar si doua in sens anti-orar) pentru transferul datelor si o structura arborescenta pentru comenzi. Latimea de banda interna a magistralei EIB este de 96 bytes pe ciclu si suporta mai mult de 100 de cereri DMA in asteptare intre SPEuri si spatiul principal de stocare (main storage).

<imgcaption image1|Diagrama bloc a arhitecturii Cell Broadband Engine>[ ]</imgcaption>

]</imgcaption>

Asa cum se observa in <imgref image1>, magistrala EIB cu acces coerent la memorie are doua interfete externe:

- Controllerul de interfata cu memoria (Memory Interface Controller (MIC)) asigura interfata dintre magistrala EIB si spatiul principal de stocare (main storage). Suporta doua canale cu memoria de tip Rambus Extreme Data Rate (XDR) I/O (XIO) si accese la memorie pe fiecare canal de 1-8, 16, 32, 64, sau 128 bytes.

- Interfata cu Cell Broadband Engine (Cell Broadband Engine Interface (BEI)) asigura managementul transferurilor de date intre magistrala EIB si dispozitivele I/O. Asigura translatarea adreselor, procesarea comenzilor, interfatarea cu magistrala si pune la dispozitie un controller intern de intreruperi. Suporta doua canale de tip Rambus FlexIO external I/O. Unul dintre aceste canale suporta doar dispozitive I/O non-coerente cu memoria. Cel de-al doilea canal poate fi configurat sa suporte atat transferuri non-coerente cat si transferuri coerente cu memoria care extind la nivel logic magistrala EIB cu cu alte dispozitive externe compatibile, cum ar fi de exemplu un alt Cell Broadband Engine.

Dezvoltarea de software in limbajul C/C++ este sustinuta de catre un set bogat de extensii de limbaj care definesc tipurile de date din C/C++ pentru operatii SIMD si contin C/C++ intrinsics (comenzi sub forma de apeluri de functii) spre una sau mai multe instructiuni de asamblare.

Aceste extensii de limbaj ofera programatorilor in C/C++ un control mai mare asupra performantelor ce pot fi obtinute din cod, fara a fi nevoie de programare in limbaj de asamblare. Dezvoltarea de software este sustinuta si de existenta:

- Unui SDK complet bazat pe Linux,

- Unui simulator de sistem si a

- Unui set bogat de librarii de aplicatii, unelte de performanta si debugging.

Power Processor Element (PPE)

Power Processor Element (PPE) este un procesor cu scop general, dual-threaded, cu arhitectura RISC pe 64 de biti conforma cu arhitectura Power, versiunea 2.02, avand setul de extensii Multimedia Vector/SIMD.

Programele scrise pentru procesorul Power 970, de exemplu, pot fi rulate pe Cell Broadband Engine fara nici o modificare.

Asa cum reiese si din Figura 6, procesorul PPE are doua unitati principale:

- Power Processor Unit (PPU).

- Power Processor Storage Subsystem (PPSS).

Power Processor Element (PPE) este responsabil de controlul general asupra sistemului si ruleaza sistemele de operare pentru toate aplicatiile ce ruleaza pe Cell Broadband Engine.

<imgcaption ppe|Diagrama Bloc a Power Processor Element (PPE)>

[ ]</imgcaption>

]</imgcaption>

Power Processor Unit (PPU) se ocupa de controlul si executia instructiunilor. Acesta contine:

- setul complet de registri Power pe 64 biti,

- 32 registri de vector pe 128 de biti,

- un cache de instructiuni de nivel 1 (L1) de 32 KB,

- un cache de date de nivel 1 (L1) de 32 KB,

- o unitate de control de instructiuni,

- o unitate pentru load and store,

- o unitate pentru numere intregi in virgula fixa,

- o unitate pentru numere in virgula mobila,

- o unitate pentru vectori,

- o unitate de predictie de ramificatie,

- o unitate de management a memoriei virtuale.

Power Processor Unit (PPU) suporta executia simultana a doua threaduri si poate fi privit ca un multiprocesor 2-way cu flux de date partajat (shared dataflow). Din punct de vedere software, acesta este vazut ca doua unitati de procesare independente.

Power Processor Storage Subsystem (PPSS) se ocupa cu cererile de acces la memorie venite din partea PPE si cererile externe pentru PPE venite din partea altor procesoare si dispozitive I/O. Acesta contine:

- un cache de nivel 2 (L2) unificat de date si instructiuni de 512 KB,

- o serie de cozi (queues),

- o unitate de interfata cu magistrala cu rol de arbitru de magistrala EIB.

Memoria este vazuta ca vector liniar de bytes indexati de la 0 la 264 - 1. Fiecare byte este identificat prin indexul sau, numit adresa, si contine o valoare. Se face cate un singur acces la memorie o data.

Cache-ul de nivel 2 (L2) si cache-urile folosite pentru translatarea adreselor tabele de management care permit controlul lor din software. Acest control software asupra resurselor de cache este in special util pentru programarea de timp real.

Synergistic Processor Elements (SPE-uri)

Fiecare dintre cele opt Synergistic Processor Elements (SPE-uri) este un procesor RISC pe 128 biti specializat in aplicatii SIMD ce necesita calcul intens asupra unor seturi multiple de date.

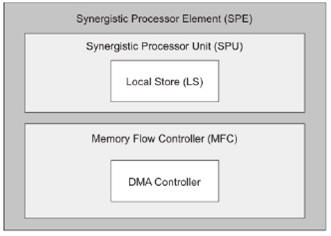

Asa cum reiese si din <imgref spe>, fiecare Synergistic Processor Element (SPE) contine doua unitati principale:

- Synergistic Processor Unit (SPU).

- Memory Flow Controller (MFC).

<imgcaption spe|Diagrama Bloc a Synergistic Processor Element (SPE)>

[ ]</imgcaption>

]</imgcaption>

Synergistic Processor Unit (SPU) se ocupa in primul rand de controlul si executia instructiunilor. Contine:

- un singur fisier de registri cu 128 registri, fiecare de 128 biti,

- o memorie locala (local store - LS) unificata (instructiuni si date) de 256 KB,

- o unitate de control a instructiunilor,

- o unitate de load and store,

- doua unitati pentru numere in virgula fixa,

- o unitate pentru numere in virgula mobila si

- o interfata DMA.

Synergistic Processor Element (SPU) implementeaza un nou set de instructiuni SIMD, numit SPU Instruction Set Architecture, care e specific pentru Broadband Processor Architecture.

Fiecare Synergistic Processor Unit (SPU) este un procesor independent cu numarator (counter) propriu de program si este optimizat pentru rularea de threaduri SPE lansate de catre Power Processor Element (PPE). Instructiunile pentru Synergistic Processor Unit (SPU) sunt aduse din memoria locala (local store – LS) iar datele sunt aduse si salvate tot in memoria locala (local store – LS). Fiind proiectata pentru a fi accesata in primul de catre SPU-ul propriu, memoria locala (local store – LS) este neprotejata si netranslatata. Memory Flow Controller (MFC) contine un controller DMA pentru transferurile DMA. Programele care ruleaza pe SPU, pe PPE sau pe alt SPU, folosesc transferuri DMA controlate de MFC pentru mutarea datelor si instructiunilor intre memoria locala (local store –LS) a SPU-urilor si spatiul principal de stocare (main storage). Spatiul principal de stocare (main storage) este format din spatiul de adrese efective care include memoria principala (main memory), memoriile locale ale altor SPE-uri si registri mapati in memorie cum ar fi registrii I/O [MMIO]. Memory Flow Controller (MFC) interfateaza Synergistic Processor Unit (SPU) cu Element Interconnect Bus (EIB), implementeaza facilitatile de rezervare bandwidth pe magistrala si sincronizeaza operatiile dintre Synergistic Processor Unit (SPU) si celelalte procesoare din sistem.

Pentru transferurile DMA, Memory Flow Controller (MFC) foloseste cozi de comenzi DMA. Dupa ce o comanda DMA a fost transmisa catre Memory Flow Controller (MFC), Synergistic Processor Unit (SPU) poate continua executia instructiunilor in timp ce Memory Flow Controller (MFC) proceseaza comenzile DMA autonom si asincron. Executia de comenzi DMA de catre Memory Flow Controller (MFC) autonom fata de executia de instructiuni de catre Synergistic Processor Unit (SPU) permite planificarea eficienta a transferurilor DMA pentru a acoperi latenta de memorie.

Fiecare transfer DMA poate avea maxim 16 KB. Totusi, doar SPU-ul asociat MFC-ului poate lansa lista de comenzi DMA. Acestea pot contine pana la 2048 transferuri DMA, fiecare de cate 16 KB. Informatia cu privire la translatarea adreselor de memorie virtuala este pusa la dispozitia MFC de catre sistemul de operare ce ruleaza pe PPE. Atributele sistemului de stocare (translatarea si protectia adreselor) sunt controlate prin tabelele de segmentare si paginare ale arhitecturii Power. Totusi exista software special pentru PPE care poate mapa adresele si memoriile locale (local store – LS) si anumite resurse MFC in spatiul de adrese din main-storage, permitand astfel PPE si altor SPU-uri din sistem sa acceseze aceste resurse.

SPE-urile ofera un mediu de operare determinist. Acestea nu au memorii cache, astfel ca nu exista cache miss-uri care sa le afecteze performanta. Regulile de planificare pe pipeline sunt simple, astfel ca performantele codului sunt usor de evaluat static. Desi memoria locala (local store – LS) este partajata intre operatiile DMA de citire si scriere, load and store si de prefetch de instructiuni, operatiile DMA sunt cumulate si pot accesa memoria locala (LS) cel mult unul din 8 cicluri. La prefetch de instructiuni sunt aduse cel putin 17 instructiuni secventiale de pe ramura tinta. In acest mod, impactul operatiilor DMA asupra timpilor de operatii load and store si de executie a programelor este limitata din designul arhitecturii.

Ordonarea byte-ilor si numerotarea bitilor

Setul de instructiuni pentru PPE este o versiune extinsa a setului de instrutiuni Power. Extensiile sunt reprezentate de catre setul de instructiuni Multimedia Vector/SIMD plus cateva adaugari si schimbari aduse setului de instructiuni Power. Setul de instructiuni pentru SPE este asemanator cu setul de instructiuni Multimedia Extins Vector/SIMD al PPE. Desi PPE si SPE-urile executa instructiuni SIMD, seturile de instructiuni sunt diferite pentru fiecare din ele (PPE si SPE), iar programele scrise pentru PPE si SPE-uri trebuie compilate cu compilatoare diferite.

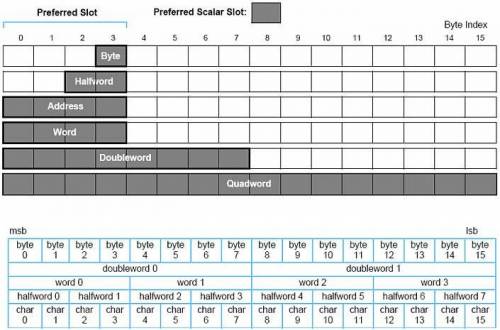

Stocarea datelor si instructiunilor in Cell Broadband Engine respecta ordonarea big-endian. Acest tip de ordonare are urmatoarele caracteristici:

- Byte-ul cel mai semnificativ este stocat la cea mai mica adresa, iar cel mai putin semnificativ byte este stocat la cea mai mare adresa.

- Numerotarea bitilor intr-un byte incepe de la cel mai semnificativ bit (bitul 0) pana la cel mai putin semnificativ bit (bitul n). Acest lucru difera fata de alte procesoare care folosesc tot ordonarea big-endian. Aceste aspecte sunt reprezentate grafic in <imgref endianness>.

<imgcaption endianness|Ordonarea Big-endian a byte-ilor si numerotarea bitilor in arhitectura Cell BE>

[ ]

</imgcaption>

]

</imgcaption>