Tetris Challenge

Acest proiect consta in implementarea unui joc Tetris cu display pe un monitor, conectat prin VGA.

Cea mai grea partea a acestui proiect este de fapt generarea semnalelor VGA, care sa fie sincronizate la microsecunda si sa fie recunoscute de catre monitor pentru a afisa ceea ce dorim.

Am plecat de la ideea implementarii unui joc pe LCD, dar am ales VGA pentru ca este util sa intelegem cum functioneaza o placa video intr-un calculator si ce calcule face pentru a genera semnalele necesare monitorului pentru a afisa o imagine clara.

Descriere generala

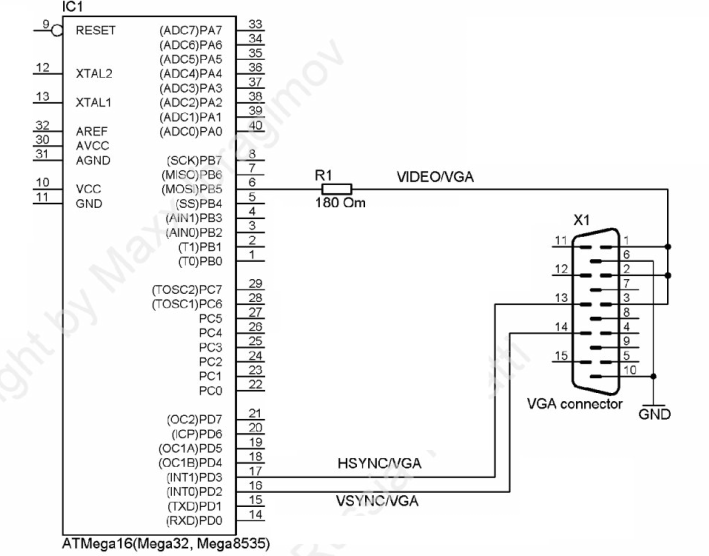

Partea de hardware este foarte simpla. Mufa VGA are 5 pini importanti, toti de intrare:

- 3 de culoare: R, G, B

- 2 pentru sincronizare: HSYNC si VSYNC.

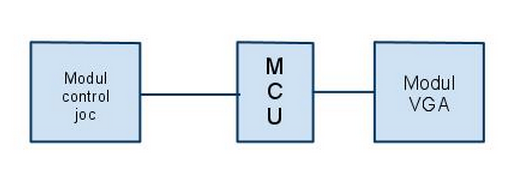

Astfel, proiectul are 3 module:

- Placa de baza, cu microcontrollerul ATmega16

- Modulul VGA, care contine mufa VGA si conexiunile cu toti cei 5 pini necesari transmisiei de imagini pe monitor

- Modulul de control al jocului, cu 4 butoane necesare miscarii caramizilor in Tetris

Hardware Design

Lista de piese

- Mufa VGA mama perpendiculara

- Rezistente: 1 x 180Ω, 4 x 1kΩ, 1 x 100kΩ

- Condensator: 10nF

- 4 butoane

Modul VGA

Transmisia semnalului video este facuta prin SPI. Am pus cei 3 pini de culoare in scurt, pentru a reda doar imagini alb-negru, si i-am conectat la portul MOSI, care a fost setat cu dubla viteza (SPI2X).

Modul Butoane

Cele 4 butoane sunt conectate la un singur pin, ADC7. Numarul butonului apasat se recunoaste prin citirea tensiunii generate de apasare, astfel:

- S1 → 5V

- S2 → 5V * 3/4

- S3 → 5V * 1/2

- S4 → 5V * 1/4

Semnalul VGA

______________________ ______________________ (video)

________| VIDEO |________| VIDEO

|-C-|----------D-----------|-E-|

__ ______________________________ _________________________ (hsync)

|_| |_|

|B|

|---------------A----------------|

A = 31.77 µs

B = 3.77 µs = timpul in care se transmite hsync

C = 1.89 µs = pauza intre hsync si transmisia pixelilor = back porch

D = 25.17 µs = timpul in care se deseneaza o linie

E = 0.94 µs = pauza dupa desenarea liniei si inainte de hsync = front porch

______________________ ______________________ (video)

________| VIDEO |________| VIDEO

|-Q-|----------R-----------|-S-|

__ ______________________________ _________________________ (vsync)

|_| |_|

|P|

|---------------O----------------|

O = 16.78 ms

P = 64.00 µs = timpul in care se transmite vsync

Q = 1.02 ms = pauza intre vsync si transmisia urmatoarei imagini = back porch

R = 15.25 ms = timpul in care se deseneaza un ecran intreg (mai multe linii)

S = 0.45 ms = pauza dupa desenarea ecranului si inainte de urmatorul vsync = front porch

Dificultatea proiectului consta in necesitatea unei sincronizari perfecte a semnalelor si respectarea tuturor timpilor descrisi mai sus. Daca un timp este putin diferit fata de timpul spcificat, monitorul nu va mai recunoaste semnalul.

Astfel, un timp de 0.94µs pe un microcontroller ATmega16 se traduce in 16MHz * 0.94µs = 15 ciclii de ceas. O astfel de sincronizare nu poate fi obtinuta cu intreruperi, cel mai bine facandu-se cu instructiuni in cod asamblare (de exemplu instructiunea NOP).

Software Design

- Platforma: Linux

- Compilator: avr-gcc (pachetul avr-libc)

- Mediu de dezvoltare: vim

- Debugger: Cel mai bine se face debug cu un osciloscop, observand semnalul scos de microcontroller

Codul a fost inspirat dintr-un proiect similar care genereaza semnale VGA.

Se foloseste de intreruperi pentru a genera intervalele de timp mai mari si de instructiuni NOP pentru a simula delay-uri foarte mici, precum cel de 0.94µs

Concluzii

- Monitoarele sunt foarte sensibile la semnalul primit si cea mai mica eroare in semnal va rezulta in nerecunoasterea acestuia

- Viteza mica a microcontrollerului ATMega16 nu permite afisarea unor rezolutii mari pe VGA

- Viteza mica a microcontrollerului ATmega16 nu face posibila sincronizarea semnalelor doar cu timere si intreruperi, uneori necesitand si scrierea unui numar fix de instructiuni de asamblare pentru a simula un delay