VGA Pong

1. Descrierea Proiectului

1.1 Descrierea generala

Proiectul presupune realizarea unui joc demonstrativ de pong folosind placuta cu microcontroler realizata in etapa anterioara si un FPGA Spartan 3E ce dispune de un port VGA (pentru monitor) de iesire si un port PS2 de intrare (pentru tastatura). Comunicarea intre FPGA si placuta se va realiza prin intermediul protocolului SPI. Placuta cu microcontroler va actiona ca master in protocolul SPI in timp ce FPGA-ul va fi pe post de slave. Microcontrolerul va interoga periodic FPGA-ul pentru input primit de la tastatura si, in functie de acest input va trimite comenzi FPGA-ului pentru a misca paleta din joc si a lovi mingea. Marea majoritate a componentelor au fost implementate pe FPGA sub forma unor module Verilog. Astfel, pe FPGA se disting urmatoarele module:

- driver-ul de VGA

- driver-ul pentru tastatura

- driver-ul pentru partea de comunicare SPI

- modulul de control al jocului ( translatia mingii, interpretarea comenzilor SPI primite de la uC, testele de ciocnire, desenarea spatiului de joc)

1.2 Descrierea implementarii pe ATMega16

Implementarea pe ATMega16 nu am mai realizat-o din cauza problemelor aparute la comunicatia SPI intre uC si FPGA. In codul pentru ATMega16 de mai jos se gaseste doar un test pentru SPI.

1.3 Descrierea implementarii pe FPGA

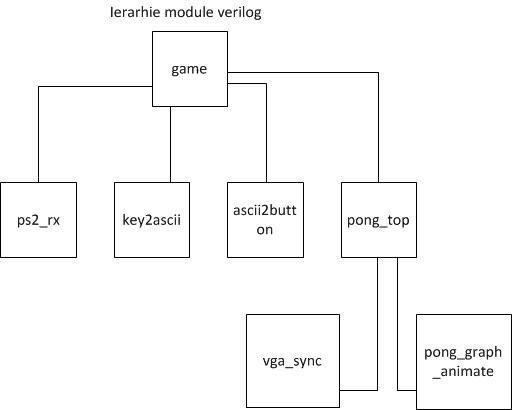

Pe FPGA am implementat practic tot jocul sub forma unor module Verilog. Modul din varful ierarhiei se numeste game si are intrarile:

- clk: sursa de ceas

- reset: butonul de reset

- ps2c: ceasul tastaturii

- ps2d: linia de date a tastaturii

si iesirile:

- rgb: pixel-ul curent de afisat

- hsync: sincronizare pe orizonatala pentru monitor

- vsync: sincronizare pe verticala pentru monitor

Acesta initializeaza si interconecteaza modulele:

- ps2_rx: controller-ul de PS2 pentru tastatura

- key2ascii: modul ce converteste scancode-ul primit de la tastatura in cod ASCII

- ascii2button: modul ce realizarea maparea intre taste si butoanele jocului

- pong_top : modulul principal pentru joc

Modulul pong_top initializeaza si interconecteaza modulele:

- vga_sync: driver-ul de VGA

- pong_graph_animate: controlerul jocului

Schema cu ierarhia modulelor se gaseste mai jos:

Pe langa aceste module, in proiectul de FPGA se mai gaseste modulul pentru driver-ul de SPI ( SPI_Slave) precum si alte module folosite in testare.

1.4 Poze reprezentative

2. Schema de principiu

3. Cod FPGA

Codul pentru FPGA-ul Spartan 3E se poate descarca de la adresa: VGAPongwithKB.rar Acesta e scris in verilog si se gaseste sub forma unui proiect Xilinx ISE 10.1 .

4. Cod microcontroller

Codul pentru uC se poate descarca de la adresa: VGAPongUC.rar

5. Concluzii si rezultate

Din nefericirea partea de comunicatie SPI intre uC si FPGA nu a mers si am fost nevoit sa implementez si controlul jocului si pe FPGA dar proiectul merge, se poate juca. Pe viitor o sa incerc sa rezolv si partea de comunicare intre uC si FPGA astfel incat sa pot folosi FPGA-ul ca un fel de placa video pentru uC.

6. Bibliografie

- Spartan 3E User Guide ug230.pdf

- Atmega 16 Datasheet doc2466.pdf

- P. Chu, FPGA Prototyping with Verilog books