## **AVR Instruction Set Manual**

#### **OTHER**

# **Instruction Set Nomenclature**

#### **Status Register (SREG)**

| SREG | Status Register                               |

|------|-----------------------------------------------|

| С    | Carry Flag                                    |

| Z    | Zero Flag                                     |

| N    | Negative Flag                                 |

| V    | Two's complement overflow indicator           |

| S    | $N \oplus V$ , for signed tests               |

| Н    | Half Carry Flag                               |

| Т    | Transfer bit used by BLD and BST instructions |

| I    | Global Interrupt Enable/Disable Flag          |

#### **Registers and Operands**

Rd: Destination (and source) register in the Register File

Rr: Source register in the Register File

R: Result after instruction is executed

K: Constant data

k: Constant address

**b:** Bit in the Register File or I/O Register (3-bit)

**s:** Bit in the Status Register (3-bit)

**X,Y,Z:** Indirect Address Register (X=R27:R26, Y=R29:R28, and Z=R31:R30)

A: I/O location address

**q:** Displacement for direct addressing (6-bit)

# **Table of Contents**

| Ins | struction Set Nomenclature                                                        | 1   |

|-----|-----------------------------------------------------------------------------------|-----|

| 1.  | I/O Registers                                                                     | 13  |

|     | 1.1. RAMPX, RAMPY, and RAMPZ                                                      | 13  |

|     | 1.2. RAMPD                                                                        |     |

|     | 1.3. EIND                                                                         | 13  |

|     | 1.4. Stack                                                                        | 13  |

|     | 1.5. Flags                                                                        | 13  |

| 2.  | The Program and Data Addressing Modes                                             | 14  |

|     | 2.1. Register Direct, Single Register Rd                                          | 14  |

|     | 2.2. Register Direct - Two Registers, Rd and Rr                                   | 15  |

|     | 2.3. I/O Direct                                                                   | 15  |

|     | 2.4. Data Direct                                                                  | 16  |

|     | 2.5. Data Indirect with Displacement                                              | 16  |

|     | 2.6. Data Indirect                                                                | 17  |

|     | 2.7. Data Indirect with Pre-decrement                                             | 17  |

|     | 2.8. Data Indirect with Post-increment                                            | 18  |

|     | 2.9. Program Memory Constant Addressing using the LPM, ELPM, and SPM Instruction  | s18 |

|     | 2.10. Program Memory with Post-increment using the LPM Z+ and ELPM Z+ Instruction | 19  |

|     | 2.11. Direct Program Addressing, JMP and CALL                                     | 19  |

|     | 2.12. Indirect Program Addressing, IJMP and ICALL                                 | 20  |

|     | 2.13. Relative Program Addressing, RJMP and RCALL                                 | 20  |

| 3.  | Conditional Branch Summary                                                        | 21  |

| 4.  | Instruction Set Summary                                                           | 22  |

| 5   | ADC – Add with Carry.                                                             | 30  |

| ٠.  | 5.1. Description                                                                  |     |

|     | 5.2. Status Register (SREG) and Boolean Formula                                   |     |

|     | 5.2. Status Register (SREG) and Boolean Formula                                   |     |

| 6.  | ADD – Add without Carry                                                           | 32  |

|     | 6.1. Description                                                                  | 32  |

|     | 6.2. Status Register (SREG) and Boolean Formula                                   | 32  |

| 7.  | ADIW – Add Immediate to Word.                                                     | 33  |

|     | 7.1. Description                                                                  | 33  |

|     | 7.2. Status Register (SREG) and Boolean Formula                                   |     |

| 8.  | AND – Logical AND                                                                 | 35  |

| ٠.  | 8.1. Description                                                                  |     |

|     | 8.2. Status Register (SREG) and Boolean Formula                                   |     |

|     | 5.2. Claras (Cogisto) (Cives) and Doubart official                                |     |

| 9.  | ANDI – Logical AND with Immediate                                                 | 36  |

|     | 9.1 Description                                                                   | 36  |

|     | 9.2.  | Status Register (SREG) and Boolean Formula             | 36   |

|-----|-------|--------------------------------------------------------|------|

| 10. | ASR   | - Arithmetic Shift Right                               | 37   |

|     |       | Description                                            |      |

|     |       | Status Register (SREG) and Boolean Formula             |      |

| 11  | BCI I | R – Bit Clear in SREG                                  | 38   |

|     |       | Description                                            |      |

|     |       | Status Register (SREG) and Boolean Formula             |      |

|     |       |                                                        |      |

| 12. |       | Bit Load from the T Flag in SREG to a Bit in Register  |      |

|     |       | Description                                            |      |

|     | 12.2. | Status Register (SREG) and Boolean Formula             | 39   |

| 13. | BRB   | C – Branch if Bit in SREG is Cleared                   | 40   |

|     | 13.1. | Description                                            | 40   |

|     | 13.2. | Status Register (SREG) and Boolean Formula             | 40   |

| 14. | BRB   | S – Branch if Bit in SREG is Set                       | 41   |

|     |       | Description                                            |      |

|     |       | Status Register (SREG) and Boolean Formula             |      |

| 4-  | DD0   | O Branch & Oams Oleaned                                | 40   |

| 15. |       | C – Branch if Carry Cleared                            |      |

|     |       | Description                                            |      |

|     | 15.2. | Status Register (SREG) and Boolean Formula             | 42   |

| 16. | BRC   | S – Branch if Carry Set                                | 43   |

|     | 16.1. | Description                                            | 43   |

|     | 16.2. | Status Register (SREG) and Boolean Formula             | 43   |

| 17. | BRE   | AK – Break                                             | 44   |

|     |       | Description                                            |      |

|     |       | Status Register (SREG) and Boolean Formula             |      |

| 10  | DDE   | O Propob if Equal                                      | 15   |

| 10. |       | Q – Branch if Equal.                                   |      |

|     |       | Description                                            |      |

|     | 10.2. | Cialus Negister (CNEG) and Boolean Formula             | 70   |

| 19. | BRG   | E – Branch if Greater or Equal (Signed)                | 46   |

|     |       | Description                                            |      |

|     | 19.2. | Status Register (SREG) and Boolean Formula             | 46   |

| 20. | BRH   | C – Branch if Half Carry Flag is Cleared               | 47   |

|     |       | Description                                            |      |

|     |       | Status Register (SREG) and Boolean Formula             |      |

| 21  | ВБП   | S Branch if Half Carry Flag is Sot                     | /1 Q |

| ۷١. |       | S – Branch if Half Carry Flag is Set                   |      |

|     |       | Description Status Register (SREG) and Boolean Formula |      |

|     |       |                                                        |      |

| 22. | . BRID – Branch if Global Interrupt is Disabled  | 49 |

|-----|--------------------------------------------------|----|

|     | 22.1. Description                                | 49 |

|     | 22.2. Status Register (SREG) and Boolean Formula | 49 |

| 23. | . BRIE – Branch if Global Interrupt is Enabled   | 50 |

|     | 23.1. Description                                | 50 |

|     | 23.2. Status Register (SREG) and Boolean Formula | 50 |

| 24. | . BRLO – Branch if Lower (Unsigned)              | 51 |

|     | 24.1. Description                                | 51 |

|     | 24.2. Status Register (SREG) and Boolean Formula | 51 |

| 25. | . BRLT – Branch if Less Than (Signed)            | 52 |

|     | 25.1. Description                                | 52 |

|     | 25.2. Status Register (SREG) and Boolean Formula | 52 |

| 26. | . BRMI – Branch if Minus                         | 53 |

|     | 26.1. Description                                | 53 |

|     | 26.2. Status Register (SREG) and Boolean Formula | 53 |

| 27. | . BRNE – Branch if Not Equal                     | 54 |

|     | 27.1. Description                                | 54 |

|     | 27.2. Status Register (SREG) and Boolean Formula | 54 |

| 28. | . BRPL – Branch if Plus                          | 55 |

|     | 28.1. Description                                | 55 |

|     | 28.2. Status Register (SREG) and Boolean Formula | 55 |

| 29. | . BRSH – Branch if Same or Higher (Unsigned)     | 56 |

|     | 29.1. Description                                | 56 |

|     | 29.2. Status Register (SREG) and Boolean Formula | 56 |

| 30. | . BRTC – Branch if the T Flag is Cleared         | 57 |

|     | 30.1. Description                                | 57 |

|     | 30.2. Status Register (SREG) and Boolean Formula | 57 |

| 31. | . BRTS – Branch if the T Flag is Set             | 58 |

|     | 31.1. Description                                | 58 |

|     | 31.2. Status Register (SREG) and Boolean Formula | 58 |

| 32. | . BRVC – Branch if Overflow Cleared              | 59 |

|     | 32.1. Description                                | 59 |

|     | 32.2. Status Register (SREG) and Boolean Formula |    |

| 33. | . BRVS – Branch if Overflow Set.                 | 60 |

|     | 33.1. Description                                |    |

|     | 33.2. Status Register (SREG) and Boolean Formula |    |

| 34. | . BSET – Bit Set in SREG.                        | 61 |

|     | 34.1. | Description                                      | 61 |

|-----|-------|--------------------------------------------------|----|

|     | 34.2. | Status Register (SREG) and Boolean Formula       | 61 |

| 35. | BST   | Bit Store from Bit in Register to T Flag in SREG | 62 |

|     |       | Description                                      |    |

|     | 35.2. | Status Register (SREG) and Boolean Formula       | 62 |

| 36. | CALI  | _ – Long Call to a Subroutine                    | 63 |

|     | 36.1. | Description                                      | 63 |

|     | 36.2. | Status Register (SREG) and Boolean Formula       | 63 |

| 37. | CBI - | - Clear Bit in I/O Register                      | 65 |

|     | 37.1. | Description                                      | 65 |

|     | 37.2. | Status Register (SREG) and Boolean Formula       | 65 |

| 38. | CBR   | - Clear Bits in Register                         | 66 |

|     | 38.1. | Description                                      | 66 |

|     | 38.2. | Status Register (SREG) and Boolean Formula       | 66 |

| 39. | CLC   | – Clear Carry Flag                               | 67 |

|     | 39.1. | Description                                      | 67 |

|     | 39.2. | Status Register (SREG) and Boolean Formula       | 67 |

| 40. | CLH   | – Clear Half Carry Flag                          | 68 |

|     | 40.1. | Description                                      | 68 |

|     | 40.2. | Status Register (SREG) and Boolean Formula       | 68 |

| 41. | CLI - | - Clear Global Interrupt Flag                    | 69 |

|     | 41.1. | Description                                      | 69 |

|     | 41.2. | Status Register (SREG) and Boolean Formula       | 69 |

| 42. | CLN   | Clear Negative Flag                              | 70 |

|     | 42.1. | Description                                      | 70 |

|     | 42.2. | Status Register (SREG) and Boolean Formula       | 70 |

| 43. | CLR   | – Clear Register                                 | 71 |

|     | 43.1. | Description                                      | 71 |

|     | 43.2. | Status Register (SREG) and Boolean Formula       | 71 |

| 44. | CLS   | – Clear Signed Flag                              | 72 |

|     | 44.1. | Description                                      | 72 |

|     | 44.2. | Status Register (SREG) and Boolean Formula       | 72 |

| 45. | CLT   | – Clear T Flag                                   | 73 |

|     | 45.1. | Description                                      | 73 |

|     | 45.2. | Status Register (SREG) and Boolean Formula       | 73 |

| 46. | CLV   | – Clear Overflow Flag                            | 74 |

|     | 46.1. | Description                                      | 74 |

|     | 46.2. Status Register (SREG) and Boolean Formula | 74 |

|-----|--------------------------------------------------|----|

| 47. | CLZ – Clear Zero Flag                            | 75 |

|     | 47.1. Description                                | 75 |

|     | 47.2. Status Register (SREG) and Boolean Formula | 75 |

| 48. | COM – One's Complement                           | 76 |

|     | 48.1. Description                                | 76 |

|     | 48.2. Status Register (SREG) and Boolean Formula | 76 |

| 49. | CP – Compare                                     | 77 |

|     | 49.1. Description                                | 77 |

|     | 49.2. Status Register (SREG) and Boolean Formula | 77 |

| 50. | CPC – Compare with Carry                         | 79 |

|     | 50.1. Description                                | 79 |

|     | 50.2. Status Register (SREG) and Boolean Formula | 79 |

| 51. | CPI – Compare with Immediate                     | 81 |

|     | 51.1. Description                                | 81 |

|     | 51.2. Status Register (SREG) and Boolean Formula |    |

| 52. | CPSE – Compare Skip if Equal                     | 83 |

|     | 52.1. Description                                | 83 |

|     | 52.2. Status Register (SREG) and Boolean Formula |    |

| 53. | DEC – Decrement                                  | 84 |

|     | 53.1. Description                                | 84 |

|     | 53.2. Status Register and Boolean Formula        | 84 |

| 54. | DES – Data Encryption Standard                   | 86 |

|     | 54.1. Description                                | 86 |

| 55. | EICALL – Extended Indirect Call to Subroutine    | 87 |

|     | 55.1. Description                                |    |

|     | 55.2. Status Register (SREG) and Boolean Formula |    |

| 56. | EIJMP – Extended Indirect Jump.                  | 88 |

|     | 56.1. Description                                |    |

|     | 56.2. Status Register (SREG) and Boolean Formula |    |

| 57. | ELPM – Extended Load Program Memory              | 89 |

|     | 57.1. Description                                |    |

|     | 57.2. Status Register (SREG) and Boolean Formula |    |

| 58. | EOR – Exclusive OR.                              | 91 |

|     | 58.1. Description                                |    |

|     | 58.2. Status Register (SREG) and Boolean Formula |    |

|     |                                                  |    |

| 59  | FMUL – Fractional Multiply Unsigned              | 92 |

|     | 59.1.  | Description                                                    | 92  |

|-----|--------|----------------------------------------------------------------|-----|

|     | 59.2.  | Status Register (SREG) and Boolean Formula                     | 92  |

| 60. | FMU    | LS – Fractional Multiply Signed                                | 94  |

|     | 60.1.  | Description                                                    | 94  |

|     |        | Status Register (SREG) and Boolean Formula                     |     |

| 61. | FMU    | LSU – Fractional Multiply Signed with Unsigned                 | 96  |

|     | 61.1.  | Description                                                    | 96  |

|     |        | Status Register (SREG) and Boolean Formula                     |     |

| 62. | ICAL   | L – Indirect Call to Subroutine                                | 98  |

|     | 62.1.  | Description                                                    | 98  |

|     | 62.2.  | Status Register (SREG) and Boolean Formula                     | 98  |

| 63. | IJMF   | P – Indirect Jump                                              | 99  |

|     | 63.1.  | Description                                                    | 99  |

|     | 63.2.  | Status Register (SREG) and Boolean Formula                     | 99  |

| 64. | IN - I | Load an I/O Location to Register                               | 100 |

|     | 64.1.  | Description                                                    | 100 |

|     | 64.2.  | Status Register (SREG) and Boolean Formula                     | 100 |

| 65. | INC    | – Increment                                                    | 101 |

|     |        | Description                                                    |     |

|     | 65.2.  | Status Register and Boolean Formula                            | 101 |

| 66. | JMP    | – Jump.                                                        | 103 |

|     | 66.1.  | Description                                                    | 103 |

|     | 66.2.  | Status Register (SREG) and Boolean Formula                     | 103 |

| 67. | LAC    | - Load and Clear                                               | 104 |

|     | 67.1.  | Description                                                    | 104 |

|     | 67.2.  | Status Register (SREG) and Boolean Formula                     | 104 |

| 68. | LAS    | – Load and Set                                                 | 105 |

|     |        | Description                                                    |     |

|     | 68.2.  | Status Register (SREG) and Boolean Formula                     | 105 |

| 69. | LAT    | – Load and Toggle                                              | 106 |

|     |        | Description                                                    |     |

|     | 69.2.  | Status Register (SREG) and Boolean Formula                     | 106 |

| 70. |        | Load Indirect from Data Space to Register using Index X        |     |

|     |        | Description                                                    |     |

|     | 70.2.  | Status Register (SREG) and Boolean Formula                     | 108 |

| 71. | LD (I  | _DD) – Load Indirect from Data Space to Register using Index Y | 109 |

|     | 71 1   | Description                                                    | 100 |

|     | 71.2. Status Register (SREG) and Boolean Formula                     | 110 |

|-----|----------------------------------------------------------------------|-----|

| 72  | . LD (LDD) – Load Indirect From Data Space to Register using Index Z | 112 |

|     | 72.1. Description                                                    | 112 |

|     | 72.2. Status Register (SREG) and Boolean Formula                     | 113 |

| 73  | . LDI – Load Immediate                                               | 115 |

|     | 73.1. Description                                                    | 115 |

|     | 73.2. Status Register (SREG) and Boolean Formula                     | 115 |

| 74  | . LDS – Load Direct from Data Space                                  | 116 |

|     | 74.1. Description                                                    | 116 |

|     | 74.2. Status Register (SREG) and Boolean Formula                     | 116 |

| 75  | . LDS (16-bit) – Load Direct from Data Space                         | 117 |

|     | 75.1. Description                                                    | 117 |

|     | 75.2. Status Register (SREG) and Boolean Formula                     | 117 |

| 76  | . LPM – Load Program Memory                                          | 118 |

|     | 76.1. Description                                                    |     |

|     | 76.2. Status Register (SREG) and Boolean Formula                     | 118 |

| 77  | . LSL – Logical Shift Left                                           | 120 |

|     | 77.1. Description                                                    |     |

|     | 77.2. Status Register (SREG) and Boolean Formula                     | 120 |

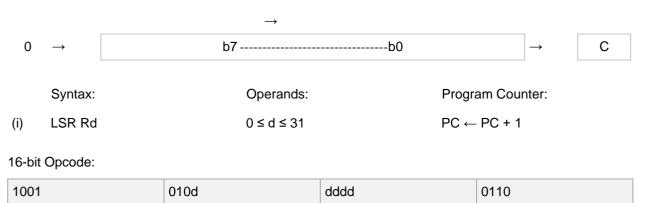

| 78  | . LSR – Logical Shift Right                                          |     |

|     | 78.1. Description                                                    |     |

|     | 78.2. Status Register (SREG) and Boolean Formula                     | 122 |

| 79  | . MOV – Copy Register                                                |     |

|     | 79.1. Description                                                    |     |

|     | 79.2. Status Register (SREG) and Boolean Formula                     |     |

| 80  | . MOVW – Copy Register Word                                          |     |

|     | 80.1. Description                                                    |     |

|     | 80.2. Status Register (SREG) and Boolean Formula                     |     |

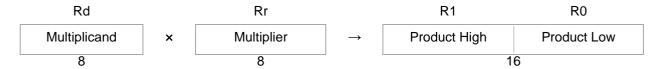

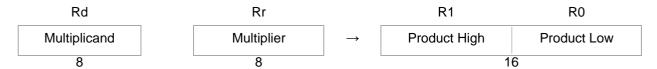

| 81. | . MUL – Multiply Unsigned                                            |     |

|     | 81.1. Description                                                    |     |

|     | 81.2. Status Register (SREG) and Boolean Formula                     | 125 |

| 82  | . MULS – Multiply Signed                                             |     |

|     | 82.1. Description                                                    |     |

|     | 82.2. Status Register (SREG) and Boolean Formula                     | 126 |

| 83  | . MULSU – Multiply Signed with Unsigned                              |     |

|     | 83.1. Description                                                    | 127 |

|     | 83.2 Status Register (SREG) and Boolean Formula                      | 127 |

| 84. | . NEG – Two's Complement                         | 129              |

|-----|--------------------------------------------------|------------------|

|     | 84.1. Description                                | 129              |

|     | 84.2. Status Register (SREG) and Boolean Formula | 129              |

| 85. | NOP – No Operation                               | 131              |

|     | 85.1. Description                                | 131              |

|     | 85.2. Status Register (SREG) and Boolean Formula | 131              |

| 86. | . OR – Logical OR.                               | 132              |

|     | 86.1. Description                                |                  |

|     | 86.2. Status Register (SREG) and Boolean Formula | 132              |

| 87. | ORI – Logical OR with Immediate                  | 133              |

|     | 87.1. Description                                |                  |

|     | 87.2. Status Register (SREG) and Boolean Formula | 133              |

| 88. | . OUT – Store Register to I/O Location           |                  |

|     | 88.1. Description                                |                  |

|     | 88.2. Status Register (SREG) and Boolean Formula | 134              |

| 89. | . POP – Pop Register from Stack                  | 135              |

|     | 89.1. Description                                |                  |

|     | 89.2. Status Register (SREG) and Boolean Formula | 135              |

| 90. | . PUSH – Push Register on Stack                  | 136              |

|     | 90.1. Description                                | 136              |

|     | 90.2. Status Register (SREG) and Boolean Formula | 136              |

| 91. | . RCALL – Relative Call to Subroutine            | 137              |

|     | 91.1. Description                                | 137              |

|     | 91.2. Status Register (SREG) and Boolean Formula | 137              |

| 92. | . RET – Return from Subroutine                   | 139              |

|     | 92.1. Description                                | 139              |

|     | 92.2. Status Register (SREG) and Boolean Formula | 139              |

| 93. | . RETI – Return from Interrupt                   | 140              |

|     | 93.1. Description                                | 140              |

|     | 93.2. Status Register (SREG) and Boolean Formula | 140              |

| 94. | . RJMP – Relative Jump                           | 142              |

|     | 94.1. Description                                | 142              |

|     | 94.2. Status Register (SREG) and Boolean Formula | 142              |

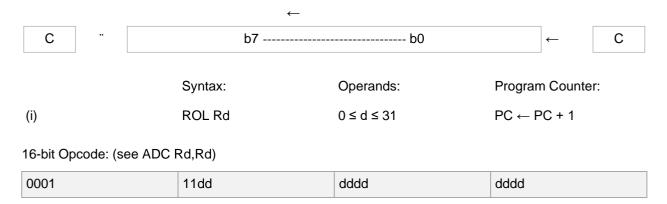

| 95. | . ROL – Rotate Left trough Carry                 | 143              |

|     | 95.1. Description                                |                  |

|     | 95.2. Status Register (SREG) and Boolean Formula | 143              |

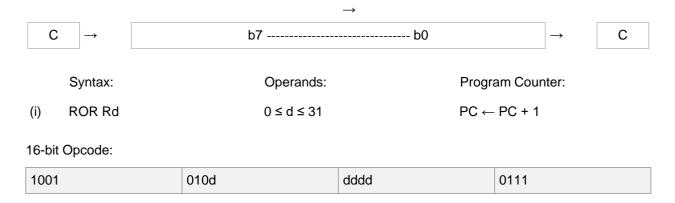

| 96  | . ROR – Rotate Right through Carry               | 115              |

| JU. | . 1. O. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.   | 1 <del>1</del> 0 |

| 96.1. Description                                                      | 145 |

|------------------------------------------------------------------------|-----|

| 96.2. Status Register (SREG) and Boolean Formula                       | 145 |

| 97. SBC – Subtract with Carry                                          | 147 |

| 97.1. Description                                                      | 147 |

| 97.2. Status Register (SREG) and Boolean Formula                       | 147 |

| 98. SBCI – Subtract Immediate with Carry SBI – Set Bit in I/O Register | 149 |

| 98.1. Description                                                      | 149 |

| 98.2. Status Register (SREG) and Boolean Formula                       | 149 |

| 99. SBI – Set Bit in I/O Register                                      | 151 |

| 99.1. Description                                                      |     |

| 99.2. Status Register (SREG) and Boolean Formula                       | 151 |

| 100. SBIC – Skip if Bit in I/O Register is Cleared                     | 152 |

| 100.1. Description                                                     | 152 |

| 100.2. Status Register (SREG) and Boolean Formula                      | 152 |

| 101. SBIS – Skip if Bit in I/O Register is Set                         | 153 |

| 101.1. Description                                                     | 153 |

| 101.2. Status Register (SREG) and Boolean Formula                      | 153 |

| 102. SBIW – Subtract Immediate from Word.                              | 154 |

| 102.1. Description                                                     | 154 |

| 102.2. Status Register (SREG) and Boolean Formula                      | 154 |

| 103. SBR – Set Bits in Register                                        | 156 |

| 103.1. Description                                                     | 156 |

| 103.2. Status Register (SREG) and Boolean Formula                      | 156 |

| 104. SBRC – Skip if Bit in Register is Cleared                         | 157 |

| 104.1. Description                                                     | 157 |

| 104.2. Status Register (SREG) and Boolean Formula                      | 157 |

| 105. SBRS – Skip if Bit in Register is Set                             | 158 |

| 105.1. Description                                                     | 158 |

| 105.2. Status Register (SREG) and Boolean Formula                      | 158 |

| 106. SEC – Set Carry Flag                                              | 159 |

| 106.1. Description                                                     | 159 |

| 106.2. Status Register (SREG) and Boolean Formula                      | 159 |

| 107. SEH – Set Half Carry Flag                                         | 160 |

| 107.1. Description.                                                    | 160 |

| 107.2. Status Register (SREG) and Boolean Formula                      | 160 |

| 108. SEI – Set Global Interrupt Flag                                   | 161 |

| 108.1 Description                                                      | 161 |

| 108.2. Status Register (SREG) and Boolean Formula                        | 161 |

|--------------------------------------------------------------------------|-----|

| 109. SEN – Set Negative Flag                                             | 162 |

| 109.1. Description                                                       | 162 |

| 109.2. Status Register (SREG) and Boolean Formula                        | 162 |

| 110. SER – Set all Bits in Register                                      | 163 |

| 110.1. Description                                                       | 163 |

| 110.2. Status Register (SREG) and Boolean Formula                        | 163 |

| 111. SES – Set Signed Flag                                               | 164 |

| 111.1. Description                                                       | 164 |

| 111.2. Status Register (SREG) and Boolean Formula                        | 164 |

| 112. SET – Set T Flag                                                    | 165 |

| 112.1. Description                                                       | 165 |

| 112.2. Status Register (SREG) and Boolean Formula                        | 165 |

| 113. SEV – Set Overflow Flag.                                            | 166 |

| 113.1. Description                                                       | 166 |

| 113.2. Status Register (SREG) and Boolean Formula                        | 166 |

| 114. SEZ – Set Zero Flag                                                 | 167 |

| 114.1. Description                                                       | 167 |

| 114.2. Status Register (SREG) and Boolean Formula                        | 167 |

| 115. SLEEP                                                               | 168 |

| 115.1. Description                                                       | 168 |

| 115.2. Status Register (SREG) and Boolean Formula                        | 168 |

| 116. SPM – Store Program Memory                                          | 169 |

| 116.1. Description                                                       | 169 |

| 116.2. Status Register (SREG) and Boolean Formula                        | 169 |

| 117. SPM #2 – Store Program Memory                                       | 171 |

| 117.1. Description                                                       |     |

| 117.2. Status Register (SREG) and Boolean Formula                        | 171 |

| 118. ST – Store Indirect From Register to Data Space using Index X       | 173 |

| 118.1. Description                                                       | 173 |

| 118.2. Status Register (SREG) and Boolean Formula                        | 174 |

| 119. ST (STD) - Store Indirect From Register to Data Space using Index Y | 175 |

| 119.1. Description                                                       |     |

| 119.2. Status Register (SREG) and Boolean Formula                        | 176 |

| 120. ST (STD) – Store Indirect From Register to Data Space using Index Z | 177 |

| 120.1. Description                                                       | 177 |

|                                                                          |     |

| 120.2 Status Register (SREG) and Boolean Formula                         | 178 |

| 121. STS – Store Direct to Data Space.            | 179 |

|---------------------------------------------------|-----|

| 121.1. Description                                | 179 |

| 121.2. Status Register (SREG) and Boolean Formula |     |

| 122. STS (16-bit) – Store Direct to Data Space    | 180 |

| 122.1. Description                                | 180 |

| 122.2. Status Register (SREG) and Boolean Formula | 180 |

| 123. SUB – Subtract Without Carry                 | 181 |

| 123.1. Description                                | 181 |

| 123.2. Status Register and Boolean Formula        | 181 |

| 124. SUBI – Subtract Immediate                    | 183 |

| 124.1. Description                                | 183 |

| 124.2. Status Register and Boolean Formula        | 183 |

| 125. SWAP – Swap Nibbles                          | 185 |

| 125.1. Description                                | 185 |

| 125.2. Status Register (SREG) and Boolean Formula | 185 |

| 126. TST – Test for Zero or Minus                 | 186 |

| 126.1. Description                                | 186 |

| 126.2. Status Register (SREG) and Boolean Formula | 186 |

| 127. WDR – Watchdog Reset.                        | 187 |

| 127.1. Description                                | 187 |

| 127.2. Status Register (SREG) and Boolean Formula | 187 |

| 128. XCH – Exchange                               | 188 |

| 128.1. Description                                | 188 |

| 128.2. Status Register (SREG) and Boolean Formula | 188 |

| 129. Datasheet Revision History                   | 189 |

| 129.1. Rev.0856L - 11/2016                        | 189 |

| 129.2. Rev.0856K - 04/2016                        |     |

| 129.3. Rev.0856J - 07/2014                        |     |

| 129.4. Rev.0856I – 07/2010                        |     |

| 129.5. Rev.0856H – 04/2009                        |     |

| 129.6. Rev.0856G – 07/2008                        |     |

| 129.7. Rev.0856F – 05/2008                        | 190 |

# 1. I/O Registers

# 1.1. RAMPX, RAMPY, and RAMPZ

Registers concatenated with the X-, Y-, and Z-registers enabling indirect addressing of the whole data space on MCUs with more than 64KB data space, and constant data fetch on MCUs with more than 64KB program space.

## 1.2. RAMPD

Register concatenated with the Z-register enabling direct addressing of the whole data space on MCUs with more than 64KB data space.

#### 1.3. **EIND**

Register concatenated with the Z-register enabling indirect jump and call to the whole program space on MCUs with more than 64K words (128KB) program space.

#### 1.4. Stack

**STACK** Stack for return address and pushed registers

**SP** Stack Pointer to STACK

# 1.5. Flags

- Flag affected by instruction

- **0** Flag cleared by instruction

- 1 Flag set by instruction

- Flag not affected by instruction

# 2. The Program and Data Addressing Modes

The AVR® Enhanced RISC microcontroller supports powerful and efficient addressing modes for access to the Program memory (Flash) and Data memory (SRAM, Register file, I/O Memory, and Extended I/O Memory). This chapter describes the various addressing modes supported by the AVR architecture. In the following figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits. To generalize, the abstract terms RAMEND and FLASHEND have been used to represent the highest location in data and program space, respectively.

**Note:** Not all addressing modes are present in all devices. Refer to the device specific instruction summary.

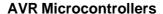

# 2.1. Register Direct, Single Register Rd

Figure 2-1. Direct Single Register Addressing

The operand is contained in register d (Rd).

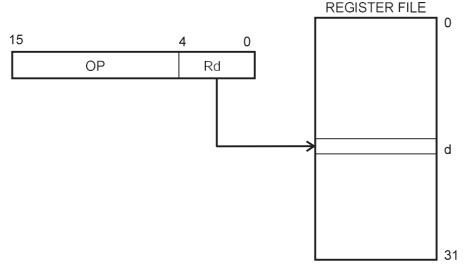

## 2.2. Register Direct - Two Registers, Rd and Rr

Figure 2-2. Direct Register Addressing, Two Registers

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

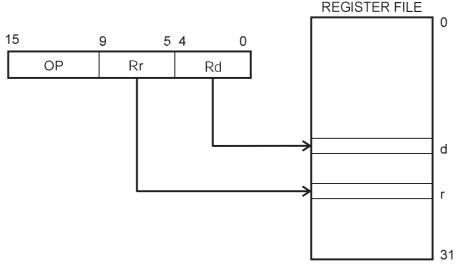

#### 2.3. I/O Direct

Figure 2-3. I/O Direct Addressing

Operand address is contained in six bits of the instruction word. n is the destination or source register address.

**Note:** Some complex AVR Microcontrollers have more peripheral units than can be supported within the 64 locations reserved in the opcode for I/O direct addressing. The extended I/O memory from address 64 to 255 can only be reached by data addressing, not I/O addressing.

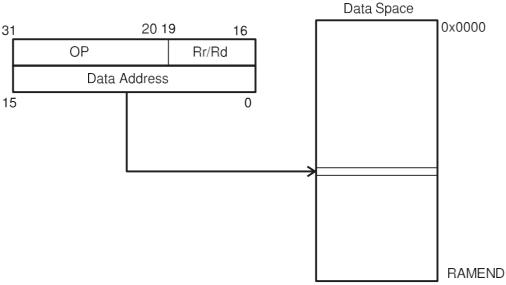

#### 2.4. Data Direct

Figure 2-4. Direct Data Addressing

A 16-bit Data Address is contained in the 16 LSBs of a two-word instruction. Rd/Rr specify the destination or source register.

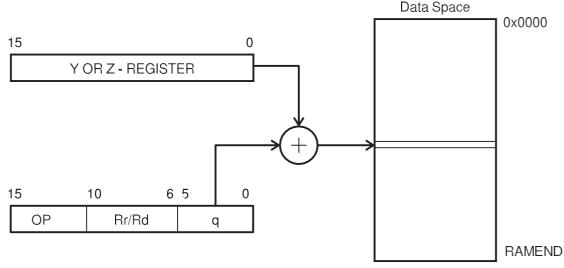

# 2.5. Data Indirect with Displacement

Figure 2-5. Data Indirect with Displacement

Operand address is the result of the Y- or Z-register contents added to the address contained in six bits of the instruction word. Rd/Rr specify the destination or source register.

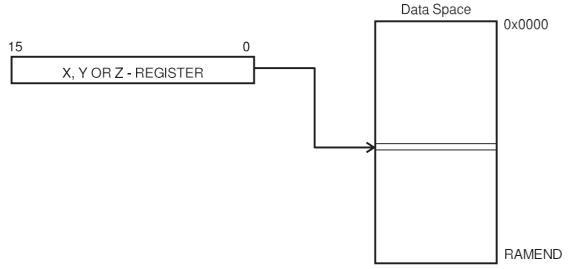

#### 2.6. Data Indirect

Figure 2-6. Data Indirect Addressing

Operand address is the contents of the X-, Y-, or the Z-register. In AVR devices without SRAM, Data Indirect Addressing is called Register Indirect Addressing. Register Indirect Addressing is a subset of Data Indirect Addressing since the data space form 0 to 31 is the Register File.

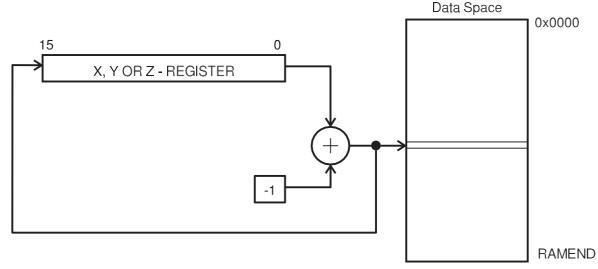

#### 2.7. Data Indirect with Pre-decrement

Figure 2-7. Data Indirect Addressing with Pre-decrement

The X,- Y-, or the Z-register is decremented before the operation. Operand address is the decremented contents of the X-, Y-, or the Z-register.

#### 2.8. Data Indirect with Post-increment

Figure 2-8. Data Indirect Addressing with Post-increment

The X-, Y-, or the Z-register is incremented after the operation. Operand address is the content of the X-, Y-, or the Z-register prior to incrementing.

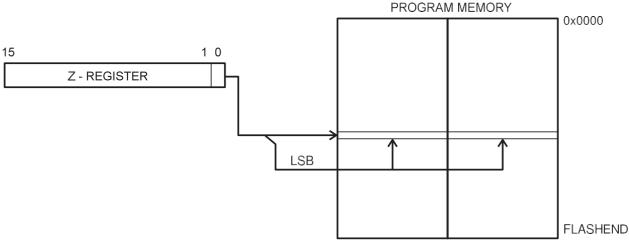

# 2.9. Program Memory Constant Addressing using the LPM, ELPM, and SPM Instructions

Figure 2-9. Program Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address. For LPM, the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1). For SPM, the LSB should be cleared. If ELPM is used, the RAMPZ Register is used to extend the Z-register.

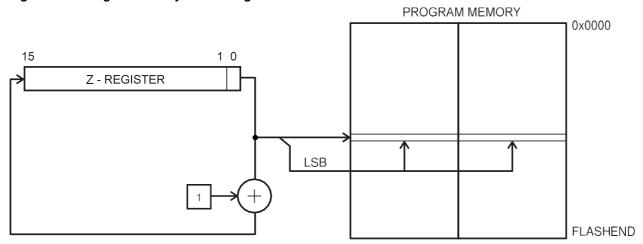

# 2.10. Program Memory with Post-increment using the LPM Z+ and ELPM Z+ Instruction

Figure 2-10. Program Memory Addressing with Post-increment

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address. The LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1). If ELPM Z+ is used, the RAMPZ Register is used to extend the Z-register.

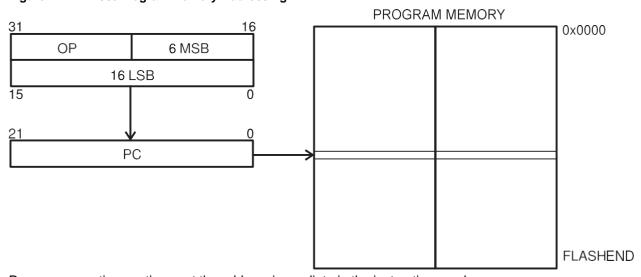

## 2.11. Direct Program Addressing, JMP and CALL

Figure 2-11. Direct Program Memory Addressing

Program execution continues at the address immediate in the instruction word.

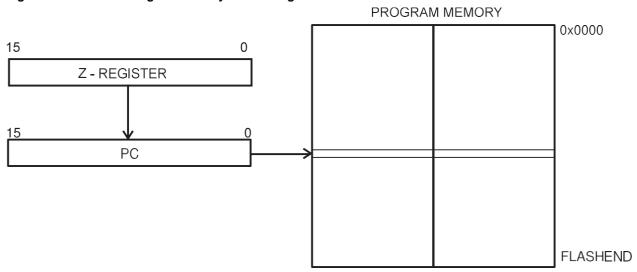

## 2.12. Indirect Program Addressing, IJMP and ICALL

Figure 2-12. Indirect Program Memory Addressing

Program execution continues at address contained by the Z-register (i.e., the PC is loaded with the contents of the Z-register).

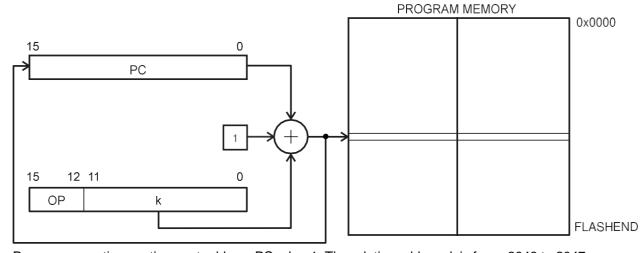

# 2.13. Relative Program Addressing, RJMP and RCALL

Figure 2-13. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is from -2048 to 2047.

# 3. Conditional Branch Summary

| Test     | Boolean               | Mnemonic            | Complementar<br>y | Boolean               | Mnemonic  | Comment  |

|----------|-----------------------|---------------------|-------------------|-----------------------|-----------|----------|

| Rd > Rr  | <b>Z•</b> (N ⊕ V) = 0 | BRLT <sup>(1)</sup> | Rd ≤ Rr           | Z+(N ⊕ V) =<br>1      | BRGE*     | Signed   |

| Rd ≥ Rr  | (N ⊕ V) = 0           | BRGE                | Rd < Rr           | (N ⊕ V) = 1           | BRLT      | Signed   |

| Rd = Rr  | Z = 1                 | BREQ                | Rd ≠ Rr           | Z = 0                 | BRNE      | Signed   |

| Rd ≤ Rr  | Z+(N ⊕ V) = 1         | BRGE <sup>(1)</sup> | Rd > Rr           | <b>Z•</b> (N ⊕ V) = 0 | BRLT*     | Signed   |

| Rd < Rr  | (N ⊕ V) = 1           | BRLT                | Rd≥Rr             | (N ⊕ V) = 0           | BRGE      | Signed   |

| Rd > Rr  | C + Z = 0             | BRLO <sup>(1)</sup> | Rd≤Rr             | C + Z = 1             | BRSH*     | Unsigned |

| Rd ≥ Rr  | C = 0                 | BRSH/<br>BRCC       | Rd < Rr           | C = 1                 | BRLO/BRCS | Unsigned |

| Rd = Rr  | Z = 1                 | BREQ                | Rd ≠ Rr           | Z = 0                 | BRNE      | Unsigned |

| Rd ≤ Rr  | C + Z = 1             | BRSH <sup>(1)</sup> | Rd > Rr           | C + Z = 0             | BRLO*     | Unsigned |

| Rd < Rr  | C = 1                 | BRLO/BRCS           | Rd≥Rr             | C = 0                 | BRSH/BRCC | Unsigned |

| Carry    | C = 1                 | BRCS                | No carry          | C = 0                 | BRCC      | Simple   |

| Negative | N = 1                 | BRMI                | Positive          | N = 0                 | BRPL      | Simple   |

| Overflow | V = 1                 | BRVS                | No overflow       | V = 0                 | BRVC      | Simple   |

| Zero     | Z = 1                 | BREQ                | Not zero          | Z = 0                 | BRNE      | Simple   |

**Note:** Interchange Rd and Rr in the operation before the test, i.e.,  $CP Rd,Rr \rightarrow CP Rr,Rd$ .

# 4. Instruction Set Summary

Several updates of the AVR CPU during its lifetime has resulted in different flavors of the instruction set, especially for the timing of the instructions. Machine code level of compatibility is intact for all CPU versions with a very few exceptions related to the Reduced Core (AVRrc), though not all instructions are included in the instruction set for all devices. The table below contains the major versions of the AVR 8-bit CPUs. In addition to the different versions, there are differences dependent of the size of the device memory map. Typically these differences are handled by a C/EC++ compiler, but users that are porting code should be aware that the code execution can vary slightly in number of clock cycles.

Table 4-1. Versions of AVR 8-bit CPU

| Name  | Device<br>Series | Description                                                                                                                                                                                      |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVR   | AT90             | Original instruction set from 1995.                                                                                                                                                              |

| AVRe  | megaAVR®         | Multiply (xMULxx), Move Word (MOVW), and enhanced Load Program Memory (LPM) added to the AVR instruction set. No timing differences.                                                             |

| AVRe  | tinyAVR®         | Multiply not included, but else equal to AVRe for megaAVR.                                                                                                                                       |

| AVRxm | XMEGA®           | Significantly different timing compared to AVR(e). The Read Modify Write (RMW) and DES encryption instructions are unique to this version.                                                       |

| AVRxt | (AVR)            | AVR 2016 and onwards. This variant is based on AVRe and AVRxm. Closer related to AVRe, but with improved timing.                                                                                 |

| AVRrc | tinyAVR          | The Reduced Core AVR CPU was developed for ultra-low pinout (6-pin) size constrained devices. The AVRrc therefore only has a 16 registers register-file (R31-R16) and a limited instruction set. |

Table 4-2. Arithmetic and Logic Instructions

| Mnemonic | Operands | Description                         |           | Ор       |               | Flags       | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|-------------------------------------|-----------|----------|---------------|-------------|----------------|------------------|------------------|------------------|

| ADD      | Rd, Rr   | Add without<br>Carry                | Rd        | <b>←</b> | Rd + Rr       | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| ADC      | Rd, Rr   | Add with<br>Carry                   | Rd        | <b>←</b> | Rd + Rr + C   | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| ADIW     | Rd, K    | Add<br>Immediate to<br>Word         | Rd        | <b>←</b> | Rd + 1:Rd + K | Z,C,N,V,S   | 2              | 2                | 2                | N/A              |

| SUB      | Rd, Rr   | Subtract<br>without Carry           | Rd        | ←        | Rd - Rr       | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| SUBI     | Rd, K    | Subtract<br>Immediate               | Rd        | ←        | Rd - K        | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| SBC      | Rd, Rr   | Subtract with Carry                 | Rd        | <b>←</b> | Rd - Rr - C   | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| SBCI     | Rd, K    | Subtract<br>Immediate<br>with Carry | Rd        | <b>←</b> | Rd - K - C    | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| SBIW     | Rd, K    | Subtract<br>Immediate<br>from Word  | Rd + 1:Rd | <b>←</b> | Rd + 1:Rd - K | Z,C,N,V,S   | 2              | 2                | 2                | N/A              |

| AND      | Rd, Rr   | Logical AND                         | Rd        | <b>←</b> | Rd • Rr       | Z,N,V,S     | 1              | 1                | 1                | 1                |

| Mnemonic | Operands | Description                                       |                                                             | Ор       |                                                  | Flags       | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|---------------------------------------------------|-------------------------------------------------------------|----------|--------------------------------------------------|-------------|----------------|------------------|------------------|------------------|

| ANDI     | Rd, K    | Logical AND with Immediate                        | Rd                                                          | ←        | Rd•K                                             | Z,N,V,S     | 1              | 1                | 1                | 1                |

| OR       | Rd, Rr   | Logical OR                                        | Rd                                                          | ←        | Rd v Rr                                          | Z,N,V,S     | 1              | 1                | 1                | 1                |

| ORI      | Rd, K    | Logical OR<br>with<br>Immediate                   | Rd                                                          | <b>←</b> | RdvK                                             | Z,N,V,S     | 1              | 1                | 1                | 1                |

| EOR      | Rd, Rr   | Exclusive OR                                      | Rd                                                          | ←        | Rd ⊕ Rr                                          | Z,N,V,S     | 1              | 1                | 1                | 1                |

| СОМ      | Rd       | One's<br>Complement                               | Rd                                                          | ←        | \$FF - Rd                                        | Z,C,N,V,S   | 1              | 1                | 1                | 1                |

| NEG      | Rd       | Two's<br>Complement                               | Rd                                                          | ←        | \$00 - Rd                                        | Z,C,N,V,S,H | 1              | 1                | 1                | 1                |

| SBR      | Rd,K     | Set Bit(s) in<br>Register                         | Rd                                                          | ←        | Rd v K                                           | Z,N,V,S     | 1              | 1                | 1                | 1                |

| CBR      | Rd,K     | Clear Bit(s) in<br>Register                       | Rd                                                          | ←        | Rd • (\$FFh -<br>K)                              | Z,N,V,S     | 1              | 1                | 1                | 1                |

| INC      | Rd       | Increment                                         | Rd                                                          | ←        | Rd + 1                                           | Z,N,V,S     | 1              | 1                | 1                | 1                |

| DEC      | Rd       | Decrement                                         | Rd                                                          | <b>←</b> | Rd - 1                                           | Z,N,V,S     | 1              | 1                | 1                | 1                |

| TST      | Rd       | Test for Zero or Minus                            | Rd                                                          | ←        | Rd • Rd                                          | Z,N,V,S     | 1              | 1                | 1                | 1                |

| CLR      | Rd       | Clear Register                                    | Rd                                                          | <b>←</b> | Rd ⊕ Rd                                          | Z,N,V,S     | 1              | 1                | 1                | 1                |

| SER      | Rd       | Set Register                                      | Rd                                                          | ←        | \$FF                                             | None        | 1              | 1                | 1                | 1                |

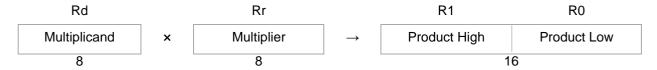

| MUL      | Rd,Rr    | Multiply<br>Unsigned                              | R1:R0                                                       | <b>←</b> | Rd x Rr (UU)                                     | Z,C         | 2              | 2                | 2                | N/A              |

| MULS     | Rd,Rr    | Multiply<br>Signed                                | R1:R0                                                       | ←        | Rd x Rr (SS)                                     | Z,C         | 2              | 2                | 2                | N/A              |

| MULSU    | Rd,Rr    | Multiply<br>Signed with<br>Unsigned               | R1:R0                                                       | <b>←</b> | Rd x Rr (SU)                                     | Z,C         | 2              | 2                | 2                | N/A              |

| FMUL     | Rd,Rr    | Fractional<br>Multiply<br>Unsigned                | R1:R0                                                       | ←        | Rd x Rr<<1<br>(UU)                               | Z,C         | 2              | 2                | 2                | N/A              |

| FMULS    | Rd,Rr    | Fractional<br>Multiply<br>Signed                  | R1:R0                                                       | <b>←</b> | Rd x Rr<<1<br>(SS)                               | Z,C         | 2              | 2                | 2                | N/A              |

| FMULSU   | Rd,Rr    | Fractional<br>Multiply<br>Signed with<br>Unsigned | R1:R0                                                       | ←        | Rd x Rr<<1<br>(SU)                               | Z,C         | 2              | 2                | 2                | N/A              |

| DES      | К        | Data<br>Encryption                                | if (H = 0) then<br>R15:R0<br>else if (H = 1)<br>then R15:R0 | <b>←</b> | Encrypt(R15:<br>R0, K)<br>Decrypt(R15:<br>R0, K) |             | N/A            | 1/2              | N/A              | N/A              |

Table 4-3. Branch Instructions

| Mnemonic | Operands | Description   |           | Ор       |            | Flags | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|---------------|-----------|----------|------------|-------|----------------|------------------|------------------|------------------|

| RJMP     | k        | Relative Jump | PC        | ←        | PC + k + 1 | None  | 2              | 2                | 2                | 2                |

| IJMP     |          | Indirect Jump | PC(15:0)  | <b>←</b> | Z          | None  | 2              | 2                | 2                | 2                |

|          |          | to (Z)        | PC(21:16) | ←        | 0          |       |                |                  |                  |                  |

| Mnemonic | Operands | Description                           |                             | Ор                   |             | Flags       | #Clocks<br>AVR       | #Clocks<br>AVRxm   | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|---------------------------------------|-----------------------------|----------------------|-------------|-------------|----------------------|--------------------|------------------|------------------|

| EIJMP    |          | Extended<br>Indirect Jump<br>to (Z)   | PC(15:0)<br>PC(21:16)       | <b>←</b><br><b>←</b> | Z<br>EIND   | None        | 2                    | 2                  | 2                | N/A              |

| JMP      | k        | Jump                                  | PC                          | <b>←</b>             | k           | None        | 3                    | 3                  | 3                | N/A              |

| RCALL    | k        | Relative Call<br>Subroutine           | PC                          | <b>←</b>             | PC + k + 1  | None        | 3 / 4 <sup>(1)</sup> | 2/3 <sup>(1)</sup> | 2/3              | 3(1)             |

| ICALL    |          | Indirect Call to (Z)                  | PC(15:0)<br>PC(21:16)       | <b>←</b>             | Z<br>0      | None        | 3/4(1)               | 2/3 <sup>(1)</sup> | 2/3              | 3 <sup>(1)</sup> |

| EICALL   |          | Extended<br>Indirect Call to<br>(Z)   | PC(15:0)<br>PC(21:16)       | ←<br>←               | Z<br>EIND   | None        | 4(1)                 | 3(1)               | 2/3              | N/A              |

| CALL     | k        | Call<br>Subroutine                    | PC                          | <b>←</b>             | k           | None        | 4/5(1)               | 3/4(1)             | 3/4              | N/A              |

| RET      |          | Subroutine<br>Return                  | PC                          | <b>←</b>             | STACK       | None        | 4/5(1)               | 4/5(1)             | 4/5              | 6(1)             |

| RETI     |          | Interrupt<br>Return                   | PC                          | <b>←</b>             | STACK       | I           | 4/5(1)               | 4/5(1)             | 4/5              | 6 <sup>(1)</sup> |

| CPSE     | Rd,Rr    | Compare,<br>skip if Equal             | if (Rd = Rr)<br>PC          | <b>←</b>             | PC + 2 or 3 | None        | 1/2/3                | 1/2/3              | 1/2/3            | 1/2              |

| СР       | Rd,Rr    | Compare                               | Rd - Rr                     |                      |             | Z,C,N,V,S,H | 1                    | 1                  | 1                | 1                |

| CPC      | Rd,Rr    | Compare with Carry                    | Rd - Rr - C                 |                      |             | Z,C,N,V,S,H | 1                    | 1                  | 1                | 1                |

| СРІ      | Rd,K     | Compare with<br>Immediate             | Rd - K                      |                      |             | Z,C,N,V,S,H | 1                    | 1                  | 1                | 1                |

| SBRC     | Rr, b    | Skip if Bit in<br>Register<br>Cleared | if (Rr(b) = 0)<br>PC        | <b>←</b>             | PC + 2 or 3 | None        | 1/2/3                | 1/2/3              | 1/2/3            | 1/2              |

| SBRS     | Rr, b    | Skip if Bit in<br>Register Set        | if (Rr(b) = 1)<br>PC        | <b>←</b>             | PC + 2 or 3 | None        | 1/2/3                | 1/2/3              | 1/2/3            | 1/2              |

| SBIC     | A, b     | Skip if Bit in I/O Register Cleared   | if (I/O(A,b) = 0) PC        | <b>←</b>             | PC + 2 or 3 | None        | 1/2/3                | 2/3/4              | 1/2/3            | 1/2              |

| SBIS     | A, b     | Skip if Bit in<br>I/O Register<br>Set | If (I/O(A,b) =1)<br>PC      | <b>←</b>             | PC + 2 or 3 | None        | 1/2/3                | 2/3/4              | 1/2/3            | 1/2              |

| BRBS     | s, k     | Branch if<br>Status Flag<br>Set       | if (SREG(s) =<br>1) then PC | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BRBC     | s, k     | Branch if<br>Status Flag<br>Cleared   | if (SREG(s) =<br>0) then PC | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BREQ     | k        | Branch if<br>Equal                    | if (Z = 1) then<br>PC       | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BRNE     | k        | Branch if Not<br>Equal                | if (Z = 0) then<br>PC       | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BRCS     | k        | Branch if<br>Carry Set                | if (C = 1) then<br>PC       | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BRCC     | k        | Branch if<br>Carry Cleared            | if (C = 0) then<br>PC       | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| BRSH     | k        | Branch if<br>Same or<br>Higher        | if (C = 0) then<br>PC       | <b>←</b>             | PC + k + 1  | None        | 1/2                  | 1/2                | 1/2              | 1/2              |

| Mnemonic | Operands | Description                              |                          | Ор       |            | Flags | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|------------------------------------------|--------------------------|----------|------------|-------|----------------|------------------|------------------|------------------|

| BRLO     | k        | Branch if<br>Lower                       | if (C = 1) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRMI     | k        | Branch if<br>Minus                       | if (N = 1) then<br>PC    | ←        | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRPL     | k        | Branch if Plus                           | if (N = 0) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRGE     | k        | Branch if<br>Greater or<br>Equal, Signed | if (N ⊕ V= 0)<br>then PC | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRLT     | k        | Branch if Less<br>Than, Signed           | if (N ⊕ V= 1)<br>then PC | ←        | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRHS     | k        | Branch if Half<br>Carry Flag<br>Set      | if (H = 1) then<br>PC    | ←        | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRHC     | k        | Branch if Half<br>Carry Flag<br>Cleared  | if (H = 0) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRTS     | k        | Branch if T<br>Flag Set                  | if (T = 1) then<br>PC    | ←        | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRTC     | k        | Branch if T<br>Flag Cleared              | if (T = 0) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRVS     | k        | Branch if<br>Overflow Flag<br>is Set     | if (V = 1) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRVC     | k        | Branch if<br>Overflow Flag<br>is Cleared | if (V = 0) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRIE     | k        | Branch if<br>Interrupt<br>Enabled        | if (I = 1) then<br>PC    | <b>←</b> | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

| BRID     | k        | Branch if<br>Interrupt<br>Disabled       | if (I = 0) then<br>PC    | ←        | PC + k + 1 | None  | 1/2            | 1/2              | 1/2              | 1/2              |

## Table 4-4. Data Transfer Instructions

| Mnemonic | Operands | Description                             |         | Ор                   |              | Flags | #Clocks<br>AVR   | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|-----------------------------------------|---------|----------------------|--------------|-------|------------------|------------------|------------------|------------------|

| MOV      | Rd, Rr   | Copy Register                           | Rd      | <b>←</b>             | Rr           | None  | 1                | 1                | 1                | 1                |

| MOVW     | Rd, Rr   | Copy Register<br>Pair                   | Rd+1:Rd | <b>←</b>             | Rr+1:Rr      | None  | 1                | 1                | 1                | N/A              |

| LDI      | Rd, K    | Load<br>Immediate                       | Rd      | <b>←</b>             | К            | None  | 1                | 1                | 1                | 1                |

| LDS      | Rd, k    | Load Direct<br>from data<br>space       | Rd      | <b>←</b>             | (k)          | None  | 2 <sup>(1)</sup> | 2 <sup>(1)</sup> | 3 <sup>(1)</sup> | 2                |

| LD       | Rd, X    | Load Indirect                           | Rd      | ←                    | (X)          | None  | 2 <sup>(1)</sup> | 1 <sup>(1)</sup> | 2 <sup>(1)</sup> | 1/2              |

| LD       | Rd, X+   | Load Indirect<br>and Post-<br>Increment | Rd<br>X | <b>←</b><br><b>←</b> | (X)<br>X + 1 | None  | 2 <sup>(1)</sup> | 1(1)             | 2 <sup>(1)</sup> | 2/3              |

| LD       | Rd, -X   | Load Indirect<br>and Pre-<br>Decrement  | X<br>Rd | <b>← ←</b>           | X - 1<br>(X) | None  | 2(1)             | 2 <sup>(1)</sup> | 2 <sup>(1)</sup> | 2/3              |

| LD       | Rd, Y    | Load Indirect                           | Rd      | ←                    | (Y)          | None  | 2(1)             | 1(1)             | 2 <sup>(1)</sup> | 1/2              |

| Mnemonic | Operands | Description                              |          | Ор       |              | Flags | #Clocks<br>AVR | #Clocks<br>AVRxm    | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|------------------------------------------|----------|----------|--------------|-------|----------------|---------------------|------------------|------------------|

| LD       | Rd, Y+   | Load Indirect<br>and Post-<br>Increment  | Rd<br>Y  | ←<br>←   | (Y)<br>Y + 1 | None  | 2(1)           | 1 <sup>(1)</sup>    | 2(1)             | 2/3              |

| LD       | Rd, -Y   | Load Indirect<br>and Pre-<br>Decrement   | Y<br>Rd  | ←<br>←   | Y - 1<br>(Y) | None  | 2(1)           | 2 <sup>(1)</sup>    | 2(1)             | 2/3              |

| LDD      | Rd, Y+q  | Load Indirect<br>with<br>Displacement    | Rd       | <b>←</b> | (Y + q)      | None  | 2(1)           | 2 <sup>(1)</sup>    | 2 <sup>(1)</sup> | N/A              |

| LD       | Rd, Z    | Load Indirect                            | Rd       | <b>←</b> | (Z)          | None  | 2(1)           | 1(1)                | 2 <sup>(1)</sup> | 1/2              |

| LD       | Rd, Z+   | Load Indirect<br>and Post-<br>Increment  | Rd<br>Z  | ←<br>←   | (Z)<br>Z+1   | None  | 2(1)           | 1(1)                | 2(1)             | 2/3              |

| LD       | Rd, -Z   | Load Indirect<br>and Pre-<br>Decrement   | Z<br>Rd  | ←<br>←   | Z - 1<br>(Z) | None  | 2(1)           | 2 <sup>(1)</sup>    | 2 <sup>(1)</sup> | 2/3              |

| LDD      | Rd, Z+q  | Load Indirect<br>with<br>Displacement    | Rd       | ←        | (Z + q)      | None  | 2(1)           | 2(1)                | 2(1)             | N/A              |

| STS      | k, Rr    | Store Direct to<br>Data Space            | (k)      | <b>←</b> | Rd           | None  | 2(1)(2)        | 2 <sup>(1)(2)</sup> | 2(1)(2)          | 1                |

| ST       | X, Rr    | Store Indirect                           | (X)      | ←        | Rr           | None  | 1(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | X+, Rr   | Store Indirect<br>and Post-<br>Increment | (X)<br>X | ←<br>←   | Rr<br>X + 1  | None  | 1(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | -X, Rr   | Store Indirect<br>and Pre-<br>Decrement  | X<br>(X) | ←<br>←   | X - 1<br>Rr  | None  | 2(1)(2)        | 2(1)(2)             | 1(1)(2)          | 2                |

| ST       | Y, Rr    | Store Indirect                           | (Y)      | ←        | Rr           | None  | 2(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | Y+, Rr   | Store Indirect<br>and Post-<br>Increment | (Y)<br>Y | ←<br>←   | Rr<br>Y + 1  | None  | 2(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | -Y, Rr   | Store Indirect<br>and Pre-<br>Decrement  | Y<br>(Y) | ←<br>←   | Y - 1<br>Rr  | None  | 2(1)(2)        | 2(1)(2)             | 1(1)(2)          | 2                |

| STD      | Y+q, Rr  | Store Indirect<br>with<br>Displacement   | (Y + q)  | ←        | Rr           | None  | 2(1)(2)        | 2(1)(2)             | 1(1)(2)          | N/A              |

| ST       | Z, Rr    | Store Indirect                           | (Z)      | ←        | Rr           | None  | 2(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | Z+, Rr   | Store Indirect<br>and Post-<br>Increment | (Z)<br>Z | ←<br>←   | Rr<br>Z + 1  | None  | 2(1)(2)        | 1(1)(2)             | 1(1)(2)          | 1                |

| ST       | -Z, Rr   | Store Indirect<br>and Pre-<br>Decrement  | Z        | ←        | Z - 1        | None  | 2(1)(2)        | 2(1)(2)             | 1(1)(2)          | 2                |

| STD      | Z+q,Rr   | Store Indirect<br>with<br>Displacement   | (Z + q)  | <b>←</b> | Rr           | None  | 2(1)(2)        | 2(1)(2)             | 1(1)(2)          | N/A              |

| LPM      |          | Load Program<br>Memory                   | R0       | ←        | (Z)          | None  | 3              | 3                   | 3                | N/A              |

| LPM      | Rd, Z    | Load Program<br>Memory                   | Rd       | ←        | (Z)          | None  | 3              | 3                   | 3                | N/A              |

| Mnemonic | Operands | Description                                                  |                 | Ор                   |                          | Flags | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|--------------------------------------------------------------|-----------------|----------------------|--------------------------|-------|----------------|------------------|------------------|------------------|

| LPM      | Rd, Z+   | Load Program<br>Memory and<br>Post-<br>Increment             | Rd<br>Z         | <b>←</b>             | (Z)<br>Z + 1             | None  | 3              | 3                | 3                | N/A              |

| ELPM     |          | Extended<br>Load Program<br>Memory                           | R0              | <b>←</b>             | (RAMPZ:Z)                | None  | 3              | 3                | 3                | N/A              |

| ELPM     | Rd, Z    | Extended<br>Load Program<br>Memory                           | Rd              | <b>←</b>             | (RAMPZ:Z)                | None  | 3              | 3                | 3                | N/A              |

| ELPM     | Rd, Z+   | Extended<br>Load Program<br>Memory and<br>Post-<br>Increment | Rd<br>(RAMPZ:Z) | <b>←</b>             | (RAMPZ:Z)<br>(RAMPZ:Z) + | None  | 3              | 3                | 3                | N/A              |

| SPM      |          | Store<br>Program<br>Memory                                   | (RAMPZ:Z)       | <b>←</b>             | R1:R0                    | None  | (4)            | (4)              | 4(3)             | N/A              |

| SPM      | Z+       | Store Program Memory and Post- Increment by 2                | (RAMPZ:Z)<br>Z  | <b>←</b>             | R1:R0<br>Z+2             | None  | (4)            | (4)              | 4(3)             | N/A              |

| IN       | Rd, A    | In From I/O<br>Location                                      | Rd              | <b>←</b>             | I/O(A)                   | None  | 1              | 1                | 1                | 1                |

| OUT      | A, Rr    | Out To I/O<br>Location                                       | I/O(A)          | <b>←</b>             | Rr                       | None  | 1              | 1                | 1                | 1                |

| PUSH     | Rr       | Push Register on Stack                                       | STACK           | <b>←</b>             | Rr                       | None  | 2              | 1(1)             | 1                | 1(1)             |

| POP      | Rd       | Pop Register from Stack                                      | Rd              | <b>←</b>             | STACK                    | None  | 2              | 2 <sup>(1)</sup> | 2                | 3(1)             |

| XCH      | Z, Rd    | Exchange                                                     | (Z)<br>Rd       | ←<br>←               | Rd<br>(Z)                | None  | N/A            | 1                | N/A              | N/A              |

| LAS      | Z, Rd    | Load and Set                                                 | (Z)<br>Rd       | ←<br>←               | Rd v (Z)<br>(Z)          | None  | N/A            | 1                | N/A              | N/A              |

| LAC      | Z, Rd    | Load and<br>Clear                                            | (Z)<br>Rd       | <b>←</b><br><b>←</b> | (\$FF – Rd) • (Z)        | None  | N/A            | 1                | N/A              | N/A              |

| LAT      | Z, Rd    | Load and<br>Toggle                                           | (Z)<br>Rd       | ←<br>←               | Rd ⊕ (Z)<br>(Z)          | None  | N/A            | 1                | N/A              | N/A              |

#### Table 4-5. Bit and Bit-test Instructions

| Mnemonic | Operands | Description            |                       | Ор          |                       | Flags     | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|------------------------|-----------------------|-------------|-----------------------|-----------|----------------|------------------|------------------|------------------|

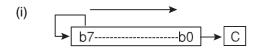

| LSL      | Rd       | Logical Shift<br>Left  | Rd(n+1)<br>Rd(0)<br>C | ←<br>←<br>← | Rd(n)<br>0<br>Rd(7)   | Z,C,N,V,H | 1              | 1                | 1                | 1                |

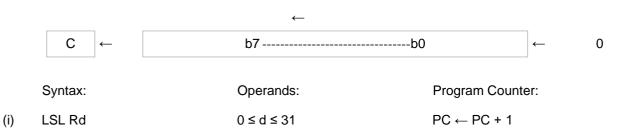

| LSR      | Rd       | Logical Shift<br>Right | Rd(n)<br>Rd(7)<br>C   | ←<br>←<br>← | Rd(n+1)<br>0<br>Rd(0) | Z,C,N,V   | 1              | 1                | 1                | 1                |

| Mnemonic | Operands | Description                           |                       | Ор                |                       | Flags     | #Clocks<br>AVR | #Clocks<br>AVRxm | #Clocks<br>AVRxt | #Clocks<br>AVRrc |

|----------|----------|---------------------------------------|-----------------------|-------------------|-----------------------|-----------|----------------|------------------|------------------|------------------|

| ROL      | Rd       | Rotate Left<br>Through<br>Carry       | Rd(0)<br>Rd(n+1)<br>C | ←<br>←<br>←       | C<br>Rd(n)<br>Rd(7)   | Z,C,N,V,H | 1              | 1                | 1                | 1                |

| ROR      | Rd       | Rotate Right<br>Through<br>Carry      | Rd(7)<br>Rd(n)<br>C   | ←<br>←<br>←       | C<br>Rd(n+1)<br>Rd(0) | Z,C,N,V   | 1              | 1                | 1                | 1                |

| ASR      | Rd       | Arithmetic<br>Shift Right             | Rd(n)                 | ←                 | Rd(n+1),<br>n=06      | Z,C,N,V   | 1              | 1                | 1                | 1                |

| SWAP     | Rd       | Swap Nibbles                          | Rd(30)                | $\leftrightarrow$ | Rd(74)                | None      | 1              | 1                | 1                | 1                |

| SBI      | A, b     | Set Bit in I/O<br>Register            | I/O(A, b)             | <b>←</b>          | 1                     | None      | 2              | 1                | 1                | 1                |

| СВІ      | A, b     | Clear Bit in I/O Register             | I/O(A, b)             | <b>←</b>          | 0                     | None      | 2              | 1                | 1                | 1                |

| BST      | Rr, b    | Bit Store from<br>Register to T       | Т                     | <b>←</b>          | Rr(b)                 | Т         | 1              | 1                | 1                | 1                |

| BLD      | Rd, b    | Bit load from<br>T to Register        | Rd(b)                 | <b>←</b>          | Т                     | None      | 1              | 1                | 1                | 1                |

| BSET     | s        | Flag Set                              | SREG(s)               | <b>←</b>          | 1                     | SREG(s)   | 1              | 1                | 1                | 1                |

| BCLR     | s        | Flag Clear                            | SREG(s)               | ←                 | 0                     | SREG(s)   | 1              | 1                | 1                | 1                |

| SEC      |          | Set Carry                             | С                     | ←                 | 1                     | С         | 1              | 1                | 1                | 1                |

| CLC      |          | Clear Carry                           | С                     | ←                 | 0                     | С         | 1              | 1                | 1                | 1                |