Table of Contents

Laboratorul 6 - Sumatoare

1. Scopul laboratorului

Scopul acestui laborator este proiectarea unor module ce implementează operații aritmetice. În acest laborator vom implementa sumatoare simple și o Unitate Aritmetico-Logică.

2. Mod de lucru

Cuvintele calculatoarelor sunt compuse din biți, deci o reprezentare facilă este în numere binare. Numărul de biți din care este compus un cuvânt determină gama de valori reprezentabilă în acel cuvânt. Spre exemplu, un cuvânt de 32 de biți poate conține valori între 0 și 232 - 1 = 4.294.967.295 (desigur, am considerat numărul ca fiind fără semn).

De asemenea, pentru a reprezenta numere negative putem folosi primul bit dintr-un cuvânt ca bit de semn. Astfel un cuvânt cu primul bit 0 este considerat număr pozitiv, iar un cuvânt cu primul bit 1 este considerat negativ. Numerele negative sunt reprezentate în cod complementar lui 2. In acest caz, un cuvânt de 32 de biți poate conține valori între -231 și 231 - 1 ([-2.147.483.648, 2.147.483.647]).

3. Sumatoare

Un sumator este un circuit digital ce realizează suma a două numere. În calculatoarele moderne ele se găsesc nu numai în unitatea aritmetică-logică (UAL) ci și în alte unități ale procesorului, fiind folosite pentru a calcula adrese, indici, etc.

3.1. Half-adder

Un half-adder este un circuit care realizează suma a doi operanzi pe un singur bit. Intrările sale sunt A și B, cei doi operanzi. El generează la ieșire două semnale: S (suma) si C (carry - transportul către următorul rang). Tabela de adevăr pentru un half-adder este prezentată în figura 3.1.

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Fig 3.1: Tabela de adevăr pentru un half-adder

3.2. Full-adder

Un full-adder este un circuit care realizează suma a doi operanzi ținând cont și de transportul din rangul inferior. Intrările sale sunt A, B (cei doi operanzi) și Cin (transportul de la rangul inferior). El generează la ieșire doua semnale: S (suma) și Cout (carry out - transportul către rangul următor). Tabela de adevăr pentru un full-adder este prezentată în figura 3.2.

| A | B | Cin | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Figura 3.2: Tabela de adevăr pentru un full-adder

3.3. Sumatorul ripple-carry

Cum în practică vom avea nevoie de numere mai mari decât 1, acestea vor fi reprezentate pe mai mulți biți. În acest caz avem o problemă: sumatoarele noastre nu pot aduna decât maxim un bit! Pentru a rezolva problema trebuie să creăm un circuit care să facă suma numerelor reprezentate pe mai mulți biți.

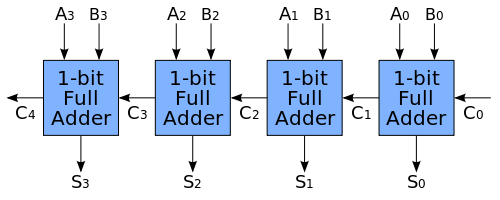

Un astfel de circuit, și cel mai simplu, este sumatorul ripple-carry. Pentru a construi un astfel de sumator pe n biți avem nevoie de fie n sumatoare full-adder (dintre care primul va avea intrarea Cin legată la 0 întotdeauna), fie de n-1 sumatoare full-adder și un half-adder (care va înlocui NUMAI acel prim full-adder fără Cin).

Conectarea lor, prezentată în figura 3.3, este una foarte simplă: ieșirea Cout a modulului de rang i va fi conectată la intrarea Cin a modulului de rang i+1. Acest fapt ne bucură în faza de proiectare, fiindcă nu avem mult de lucru, însă un astfel de sumator este încetinit de faptul că modulul de rang i trebuie să aştepte modulul de rang i-1 sa îşi termine executia pentru a afla cât este Cin, iar cel de rang i-1 la rândul său trebuie să îl aștepte pe cel de rang i-2 s.a.m.d.

Figura 3.3: Un sumator ripple-carry pe 4 biți

4. Unitatea Aritmetico-Logică

Unitatea Aritmetico-Logică este o componentă care se ocupă de aproape toate calculele numerice necesare unui procesor. În ciclul de prelucrare a instrucţiunilor, în diverse etape procesorul are nevoie de rezultatele unor calcule, fie că sunt solicitate de o intrucţiune explicită cum este add din limbajul de asamblare, fie dintr-un motiv intern (de exemplu adresa absolută a unei date se calculează în funcţie de segment şi offset, ceea ce implică nevoia unor calcule).

O UAL poate fi proiectată să execute, în principiu, orice operație. Totuși, cu cât operațiile devin mai complexe, UAL devine mai scumpă, ocupă mai mult loc și disipă mai multă căldură. Operațiile care sunt, în general, suportate de toate UAL sunt:

- Operații logice: AND, OR, NOT, XOR, NOR, NAND, etc.

- Operații de shift: shift stânga, shift dreapta, shift circular, etc.

- Operații aritmetice: adunare, scădere, înmulțire (nu toate), împărțire (nu toate).

TL;DR

- Cuvintele calculatorului sunt compuse din biți, prin urmare, cuvintele sunt doar niște valori.

- Convenție (Complement față de 2):

- pozitive - primul bit este 0

- negative - primul bit este 1

- Sumator = circuit digital care realizează suma a două numere

- Half-adder = realizează suma a doi operanzi pe un singur bit

- Full-adder = realizează suma a doi operanzi pe un singur bit ținând cont și de transportul din rangul inferior

- Ripple-carry = sumator pe n biți realizat din n sumatoare 'full-adder' cascadate

- Cin(i+1) = Cout(i)

- Cin(0) = 0

- Unitatea Aritmetică Logică se ocupă de aproape toate calculele cerute de procesor, solicitate de o instrucțiune explicită sau necesară intern.

- Instrucțiuni uzuale:

- Operații Logice: AND, OR, NOT, XOR, NOR, NAND, etc.

- Operații de shift: shift stânga, shift dreapta, shift circular, etc.

- Operații aritmetice: ADD, SUB, MUL (nu toate), DIV (nu toate).

Exerciții

- (4p) Implementați un half-adder și un full-adder fără să folosiți operatorul '+' din Verilog.

- (2p) Implementarea half-adder se va face în fișierul

task0.vla oricare dintre din următoarele nivele:- la nivel structural

- la nivel flux de date

- la nivel procedural

- (2p) Implementarea full-adder se va face în fișierul

task1.vutilizând două instanțe ale half-adder-ului implementat la subpunctul anterior.

- (2p) Implementați un sumator ripple-carry pe 8 biți în fișierul

task2.v.- !!! Pentru implementare folosiți modulele de la punctul precedent.

- (2p) Implementați un scăzător pe 8 biti în fișierul

task3.v, pornind de la modulul de la punctul precedent. - (2.5p) Implementați un modul UAL

task4.vcu intrări pe 8 biți. Modulul va primi la intrare 2 numere (i_w_a și i_w_b) și indicatorul unei operații ce se va efectua asupra numerelor (i_w_op_sel). Ieșirea modului (o_w_result) va fi un număr pe 8 biți ce reprezintă rezultatul aplicării operației asupra numerelor i_w_a și i_w_b. Pentru valorile lui i_w_op_sel avem următoarele operații:- (0.5p) 0 :

AND - (0.5p) 1 :

XOR - (0.5p) 2 :

OR - (0.5p) 3 :

ADD(folosițitask2) - (0.5p) 4 :

SUB(folosițitask3)